#KV58学习笔记-GPIO

想要使用GPIO,先需要配置时钟和PORT端口。时钟的配置由SIM模块控制。

SIM:提供系统控制和芯片配置寄存器,它有如下功能:

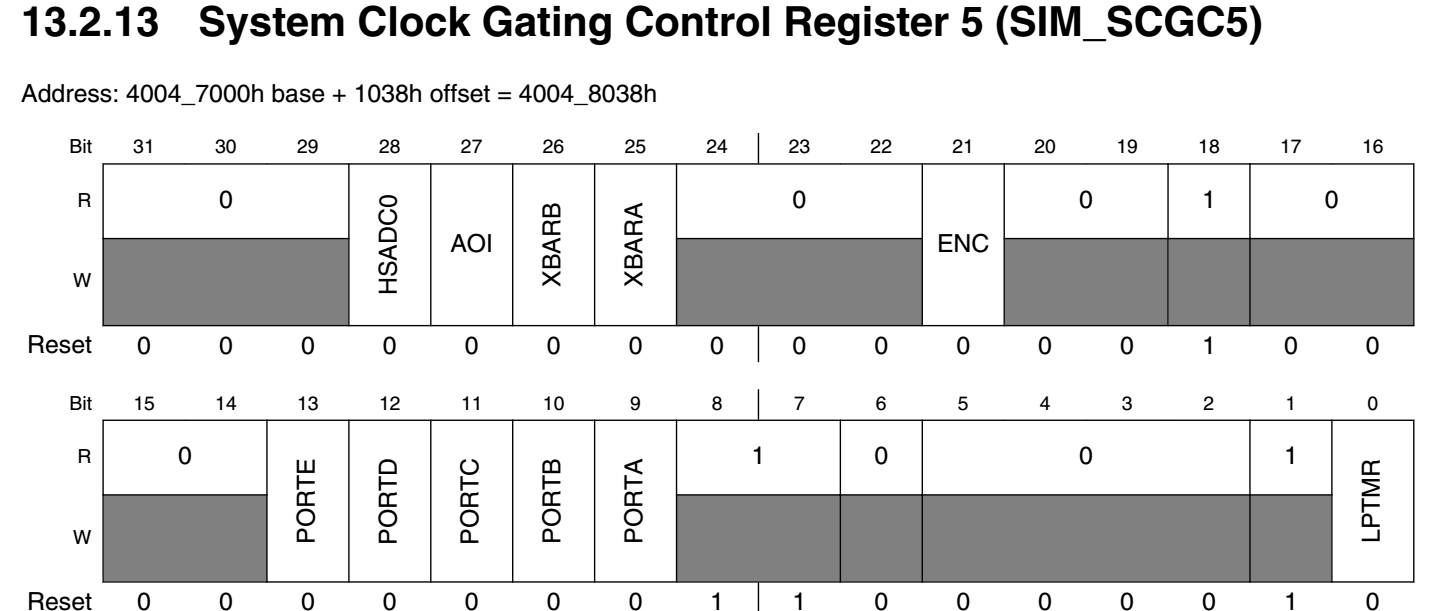

SIM具有多个寄存器来进行多个外设的配置,PORT的配置由SIM_SCGC5管理。

- void port_init(PTXn_e ptxn, PORT_CFG cfg )

{

SIM_SCGC5 |= (SIM_SCGC5_PORTA_MASK << PTX(ptxn)); //开启PORTx端口

PORT_ISFR_REG(PORTX_BASE(ptxn)) = (1<<PTn(ptxn)); // 清空标志位

PORT_PCR_REG(PORTX_BASE(ptxn), PTn(ptxn)) = cfg;

// 复用功能 , 确定触发模式 ,开启上拉或下拉电阻

}

这个函数第一行语句对SIM_SCGC5相应位置写1开启对应PORT时钟,第二第三条语句对ISFR和PCR操作,清除标志位,配置触发模式,其中触发模式使用枚举方便配置

typedef enum PORT_CFG

{

IRQ_ZERO = PORT_PCR_IRQC(0x08), //低电平触发

IRQ_RISING = PORT_PCR_IRQC(0x09), //上升沿触发

IRQ_FALLING = PORT_PCR_IRQC(0x0A), //下降沿触发

IRQ_EITHER = PORT_PCR_IRQC(0x0B), //跳变沿触发

IRQ_ONE = PORT_PCR_IRQC(0x0C), //高电平触发//DMA请求

DMA_RISING = PORT_PCR_IRQC(0x01), //上升沿触发

DMA_FALLING = PORT_PCR_IRQC(0x02), //下降沿触发

DMA_EITHER = PORT_PCR_IRQC(0x03), //跳变沿触发//功能复用

ALT0 = PORT_PCR_MUX(0x00),

ALT1 = PORT_PCR_MUX(0x01), //GPIO

ALT2 = PORT_PCR_MUX(0x02),

ALT3 = PORT_PCR_MUX(0x03),

ALT4 = PORT_PCR_MUX(0x04),

ALT5 = PORT_PCR_MUX(0x05),

ALT6 = PORT_PCR_MUX(0x06),

ALT7 = PORT_PCR_MUX(0x07),HDS = PORT_PCR_DSE(0x01), //输出高驱动能力

OD = PORT_PCR_ODE(0x01), //漏极输出

PF = PORT_PCR_PFE(0x01), //带无源滤波器

SSR = PORT_PCR_SRE(0x01), //输出慢变化率//下拉上拉选择

PULLDOWN = 0x02 << PORT_PCR_PS_SHIFT, //下拉

PULLUP = 0x03 << PORT_PCR_PS_SHIFT, //上拉

} PORT_CFG;

对PCR寄存器配置使用枚举体,方便书写

void gpio_init (PTXn_e ptxn, GPIO_CFG cfg, uint8 data)

{

port_init(ptxn,ALT1); //复用管脚为GPIO功能

//端口方向控制输入还是输出

if( cfg == GPI )

{//设置端口方向为输入 GPIO_PDDR_REG(GPIOX_BASE(ptxn)) &= ~(1 << PTn(ptxn)); // GPIO PDDR 管脚号 清0,即对应管脚配置为端口方向输入}

else

{//设置端口方向为输出 GPIO_PDDR_REG(GPIOX_BASE(ptxn)) |= (1 << PTn(ptxn)); // GPIO PDDR 管脚号 置1,即对应管脚配置为端口方向输出 //端口输出数据 if(data == 0) { GPIO_PDOR_REG(GPIOX_BASE(ptxn)) &= ~(1 << PTn(ptxn)); // GPIO PDOR 管脚号 清0,即对应管脚配置为端口输出低电平 } else { GPIO_PDOR_REG(GPIOX_BASE(ptxn)) |= (1 << PTn(ptxn)); // GPIO PDOR 管脚号 置1,即对应管脚配置为端口输出高电平 }}

}

剩下的GPIO配置就是配置输入输出,由PDDR寄存器控制,配置输出时,PDOR控制电平输出状态